Universidad, Ciencia y Tecnología

versión impresa ISSN 1316-4821versión On-line ISSN 2542-3401

uct v.10 n.39 Puerto Ordaz jul. 2006

Metodología de implementación de un controlador PID difuso en una FPGA

López R., Leonardo J.1, Franco M., Zulay E.2, Pateti M., Antonio S.3

Universidad Nacional Experimental Politécnica Antonio José de Sucre Vice-Rectorado Puerto Ordaz. Departamento de Ingeniería Electrónica

1sunmessenger@cantv.net

2zfranco@poz.unexpo.edu.ve

3apateti@poz.unexpo.edu.ve

Resumen

En este trabajo se describe una metodología para diseñar un Controlador PID Difuso para ser implementado en un arreglo de compuertas lógicas programables (FPGA). El desarrollo del controlador se basó en el comportamiento dinámico (en un sistema de control simulado) del error, diferencial del error y la salida de mencionado sistema. Se describen las diferentes fases de la metodología, además de mencionar las herramientas de diseño asistido por computadora en las fases que lo requieren. Se describe el diseño a implementar en la FPGA en el estándar VHDL. Finalmente se inserta el Controlador PID Difuso en un sistema de control de nivel, el cual ilustra la aplicación de cada fase de la metodología visto de una manera real. Se pueden implementar Controladores PID Difusos en plataformas de poca capacidad matemática y de memoria, con respuesta aceptables en corto tiempo.

Palabras clave: Controlador PID Difuso/ VHDL/ FPGA.

I. INTRODUCCIÓN.

Las teorías de Lógica Difusa (Fuzzy Logic) fueron enunciadas en 1965 por Lotfi A. Zadeh, como una herramienta matemática para manejar imprecisiones del razonamiento humano. La principal aplicación de la Lógica Difusa es en el campo de control [1], en el que el modelo matemático del proceso es desconocido, muy complejo o variante en el tiempo; por lo tanto, el conocimiento de un experto es necesario para controlar el sistema. La característica más resaltante de la Lógica Difusa es la capacidad de expresar el conocimiento en una forma lingüística, lo que permite que un sistema pueda ser descrito por simples reglas humanas.

Un FPGA consiste de un arreglo de bloque lógico configurables e interconexiones programables [2]. Su ventaja estriba en que tanto los bloques como las interconexiones se pueden reconfigurar. Como una alternativa al incremento de los sistemas de cómputos, los arreglos de compuertas lógicas programables se han usado recientemente con éxito en muchas aplicaciones. Dado que los algoritmos se implantan a nivel de circuitos, el rendimiento observado en varias aplicaciones es superior al que se obtiene mediante sistemas de cómputos de propósito general. Debido a las ventajas que se presentaron en los párrafos anteriores, en este trabajo se describe una metodología para implementar un Controlador PID Difuso en un Arreglo de Compuertas Lógicas Programables (FPGA). Se utiliza Lógica Difusa porque reduce significativamente la carga computacional, lo que conduce a utilizar menos recursos internos en la FPGA y ofrece soluciones aceptables en corto tiempo.

El procedimiento que permitió lograr los objetivos de la presente investigación son los siguientes: estrategia de diseño, se describen cada una de las fases de la metodología propuesta, se muestra una aplicación de la metodología propuesta a un sistema real.

II.- DESARROLLO

1.- Estrategia de diseño.

La tendencia actual de diseño de circuitos integrados, es que éstos realicen todas las funciones que se requieran en un chip, por tal motivo se implementa en la FPGA el algoritmo de adquisición de datos, pre-procesado, algoritmo difuso, post-procesado y determinación de la salida del sistema, así como también el módulo de comunicación con un computador para registrar los valores de la variable a controlar e insertar el punto de operación del sistema.

2.- Metodología desarrollada para la implementación de un Controlador PID Difuso en una FPGA

Para desarrollar el Controlador PID Difuso se define la estructura a implementar en la FPGA.

Se obtienen los parámetros que caracterizan el funcionamiento del proceso, de tal manera, que la simulación que se realiza tenga un alto grado de certeza con el proceso real. Después de hallar los parámetros que caracterizan el funcionamiento del proceso, se procede a realizar la simulación del proceso con un PID convencional. De ella se obtiene el comportamiento dinámico del error, de la diferencia del error y de la salida, que luego permitirán definir la base de reglas del controlador difuso. Se establecen los parámetros estructurales del controlador PID difuso. Establecidos los parámetros estructurales, se realiza una simulación estática (fuera del proceso) del controlador, y así se puede observar si se obtuvo un comportamiento deseado. Esto se realiza mediante un análisis de la superficie de control. Para definir los parámetros de entonación se realiza la simulación del controlador de manera dinámica, esto consiste en remplazar el Controlador PID convencional por el PID difuso utilizando parámetros de entonación iniciales, luego se ajustan los parámetros de entonación mediante un criterio de desempeño, como es la integral del error absoluto (IAE) y el índice de oscilación en la salida (ios).

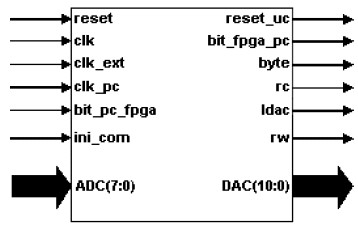

Se definen y describen las entradas y salidas necesarias para implementar en la FPGA el Controlador PID Difuso, así como también el módulo de comunicación con un computador para registrar los valores de la variable a controlar e insertar el punto de operación del sistema. Luego se realiza la descripción del hardware bajo el estándar VHDL (VHSIC Hardware Description Language, VHSIC: Very High Speed Integrated Circuit). Se realiza la síntesis, que consiste en verificar la correcta sintaxis de los ficheros que están en código VHDL, mapear el código en lógica estándar, optimizar el diseño en velocidad ó área de acuerdo a la FPGA a utilizar, para crear un archivo.XNF. Se realiza la implementación, que consiste en mezclar los archivos.XNF (generado de la síntesis) y archivo.UCF que contiene información de las entradas y salidas del diseño. Luego agrupa la lógica estándar en componentes físicos, como bloques lógicos configurables (CLBs) y bloques de entrada y salida configurables (IOBs), después genera un archivo.BIT el cual configura la FPGA de acuerdo al diseño.

Verificación del correcto funcionamiento del controlador.

3.- Aplicación

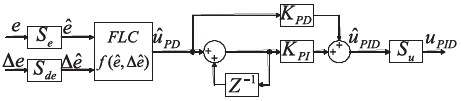

Para este trabajo se utiliza la estructura propuesta en [3] mostrada en la Figura 1.

Figura1. Estructura de un Controlador PID Difuso de acción directa.

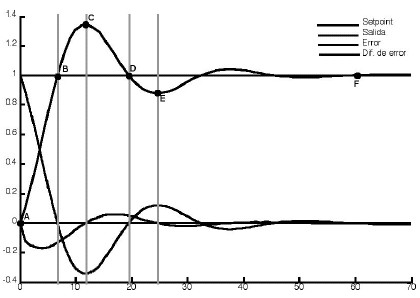

Para obtener el comportamiento dinámico del controlador PID convencional se utilizó la herramienta Simulink [4] de Matlab 6.0 como se muestra en la Figura 2.

Figura 2: Error, diferencial del error y salida del sistema.

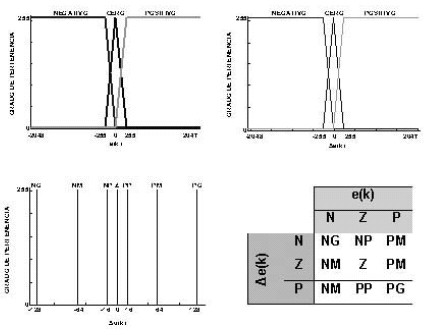

Se establecen los parámetros estructurales del controlador:

Figura 3. Entradas, Salida y base de Reglas del Controlador Difuso.

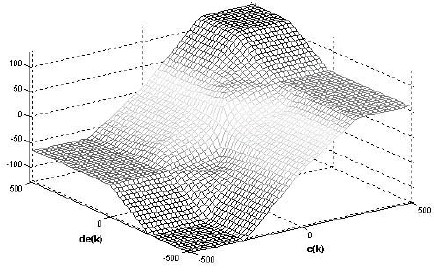

Se realiza la simulación estática utilizando un [5] y Fuzzy Logic Toolbox [6] ambos de MatLab 6.0 y se obtiene la superficie de control que se muestra en la Figura 4.

Figura 4. Simulación Estática del Controlador Difuso.

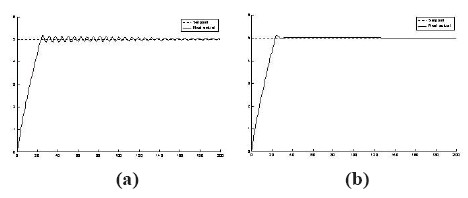

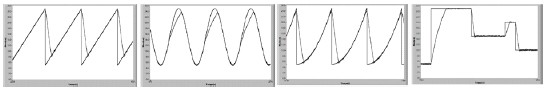

En la Figura 5.a se muestran los resultados de la simulación con los parámetros de entonación iniciales, y en la Figura 5.b se observa la salida del sistema usando los parámetros de entonación óptimos encontrados. Ambas simulaciones se realizaron utilizando Simulink de Matlab 6.0.

Figura 5.a.-Evolución del nivel con los parámetros iniciales de entonación. 5.b.-Evolución del nivel con los parámetros óptimos de entonación.

La descripción en VHDL [7] del diseño se realiza bajo el esquema que se presenta en la Figura 6.

Figura 6. Esquema del diseño en VHDL.

El código VHDL se escribe en el programa Webpack 6.1i, y se simula en ModelSim XE II 5.7c.

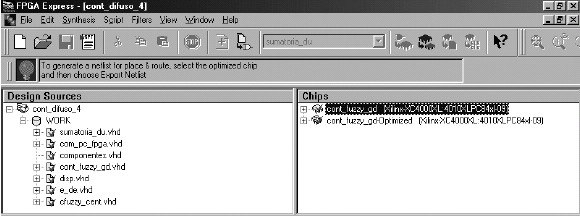

Se realiza la síntesis utilizando el software FPGA Express 4.1i de Xilinx Foundation y se generara el archivo .XNF. (Figura 7)

Figura 7. Síntesis en FPGA Express.

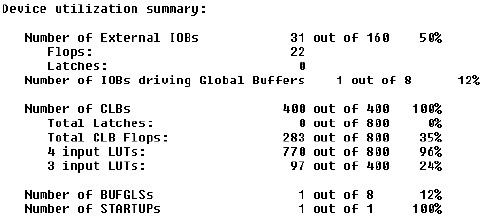

Se realiza la implementación utilizando el software Desing Manager el cual genera el archivo .BIT para configurar la FPGA XC4010XL [8] (inserta en el sistema de desarrollo XS4010XL+ [9]) y también el reporte de la cantidad de recursos utilizada. (Figura 8)

Figura 8. Reporte de la implementación.

Verificación del funcionamiento del controlador. En esta fase se inserta la FPGA al proceso de control real, y se expone una aplicación práctica de Controlador PID Difuso en un sistema de control de nivel.

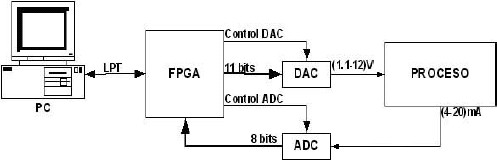

Figura 9. Sistema implementado.

El sistema de control implementado (ver Figura 9) consta de los siguientes elementos: la FPGA, el proceso de control de nivel, el computador, el bloque ADC constituido por el circuito acondicionador de la señal proveniente del proceso, y convertidor A/D y bloque DAC constituido por el convertidor D/A y el amplificador de corriente y voltaje.

El proceso de control de nivel consta de dos tanques. El primer tanque tiene una base de 10cmx10cm y una altura de 40cm, también contiene los siguientes elementos: un medidor de nivel visual (medida directa), una válvula de paso de media pulgada ubicada en la parte inferior de unas de las paredes del tanque (que vierte agua al segundo tanque) y un sensor transmisor de presión diferencial inteligente, que se calibra para que tenga una salida de (4-20)mA en un rango de medida de (0-25,5)cm. El segundo tanque tiene las siguientes dimensiones: 20cmx20cm de base y una altura de 20cm, está ubicado por debajo del primer tanque y funciona como un contenedor, en la parte inferior de una de las paredes está ubicada una bomba que retorna el agua al primer tanque, cuyo caudal de salida depende proporcionalmente a una tensión de 1,1V a 12V. El resultado de esta fase se observa en la Figura 10 en la que se muestra como evoluciona el nivel del agua ante las diferentes señales de prueba (rampa, parabólica, senoidal) y cambios en la referencia con interferencias. Estas señales fueron tomadas a través de una interfase usuario sistema realizado bajo LabVIEW 6.0i [10] [11].

Figura 10. Resultado del Controlador PID Difuso implementado en la FPGA.

4.- Discusión de resultados

Del análisis de la Figura 2, se obtiene la base de reglas del Controlador Difuso de la siguiente manera: cuando el error (e(k)) es positivo (P) y el diferencial del error es negativo (de(k)) entonces la salida (du(k)) tiene un valor incremental positivo mediano (PM) para alcanzar el punto de operación; en caso contrario, si e(k) es N y de(k) es P entonces du(k)) es negativo mediano (NM). Lo anterior menciona la deducción de dos reglas, procedimiento que se utiliza para hallar las demás reglas. Como se observa en la Figura 4, cuando e(k)es positivo entonces du(k) es positivo; de manera contraria cuando e(k) es negativo también lo es du(k); pero la amplitud de la salida du(k) dependerá del valor de la entrada de(k) , si e(k) es positivo y de(k) es positivo la salida del sistema se aleja de la referencia con valores inferiores a ella. Por lo tanto la respuesta del controlador es enviar una salida positiva grande. En caso de que e(k) sea positivo y de(k) negativo, la salida del sistema se acerca a la referencia con valores inferiores a ella, por lo tanto el controlador envía una respuesta positiva mediana y su amplitud disminuye a medida que la salida del sistema se acerca al punto de operación. De manera semejante ocurre cuando e(k) es negativo, pero los casos tienen signos opuestos. El controlador tiene un efecto predictivo ya que al evaluar la tendencia del error le asigna una amplitud lo que trae como resultado que minimiza los sobreimpulsos en la salida del sistema. También se observa que la acción de control tiene efecto en un margen cercano a cero.

Analizando la repuesta del controlador, Figura 5.a, se observa que la salida del sistema tiene muchas oscilaciones, por lo que es necesario agregarle un efecto predictivo en la entonación para reducir las oscilaciones. Este efecto se logra variando los parámetros de entonación.

El resultado de la fase de verificación se observa en la Figura 10, que muestra cómo el nivel sigue la referencia impuesta por el usuario y mantiene el punto de operación sin importar que exista interferencia en el proceso.

III.- CONCLUSIONES

1. Es posible implementar un Controlador PID Difuso en una FPGA XC4010XL, con datos de entrada y salida de 11 bits; además de manejar la comunicación y convertidores A/D y D/A.

2. MatLab 6.0 contiene todas las herramientas para diseñar y simular, de manera estática y dinámica, un Controlador PID Difuso.

3. Las herramientas Toolbox Fuzzy Logic simula el Controlado PID Difuso en una forma continua.

4. Lo anterior no se aplica a la realidad porque la plataforma de implementación es de naturaleza digital, y por ello se recurrió a los ficheros.m que emulan el comportamiento discreto.

5. El Controlador PID Difuso tiene un tiempo de respuesta rápido, un sobreimulso mínimo y sigue fielmente la referencia, condición deseable en un sistema de control.

6. La arquitectura del controlador implementada sobre un dispositivo reconfigurable, le da naturaleza abierta para cambios con miras a aumentar el rango de control y comunicación con la PC, así como aumentar ó disminuir el efecto predictivo del controlador a través de Sde y KPD.

IV.- REFERENCIAS

1. Del Brío, B y Sanz, A., Redes Neuronales y Sistemas Borrosos, 2ª. edición, Madrid, RA-MA, 2001, 399pp. [ Links ]

2. Franco, Z, Tesis de Maestría, Realización mediante FPGA de filtro pasa banda con retroalimentación para modulación FSK, UNEXPO, Vicerrectorado de Puerto Ordaz. 2002, 83pp. [ Links ]

3. LYON, E, Tesis de Maestría, Desarrollo de Controladores Fuzzy PID, UNEXPO Vicerrectorado de Puerto Ordaz. 2003, 138pp. [ Links ]

4. Simulink. Simulation and Model-Besed Desing, TheMatWo r k s I n c . , Ve r s i o n 5 , J u l y 2 0 0 2. www.mathworks.com/access/helpdesk/help/pdf_doc/simulink/sl_using.pdf. [ Links ]

5.MATLAB. T h e L a n g u a g e o f t e c h n i c a l Computing.www.mathworks.com/access/helpdesk/help/pdf_doc/matlab/matlab_prog.pdf. [ Links ]

6. Fuzzy Logic Toolbox for use with MATLAB, The MatWorks I n c . , Ve r s i ó n 2 , S e p t e m b e r 2000. www.mathworks.com/access/helpdesk/help/pdf_doc/f uzzy/fuzzy.pdf. [ Links ]

7. Perry, R VHDL, 3ª. edición, New York, McGraw-Hill, 1997, 493pp. [ Links ]

8. XC4000E and XC4000X Series Field Programmable Gate A r r a y s , X i l i n x C o . , Ve r s i o n 1 . 6 , M a y 1999. www.xilinx.com/bvdocs/publications/4000.pdf. [ Links ]

9. XS40, XSP Board V1.4. User Manual, XESS Corp., Version 1.4, September 1999. www.xess.com/manuals/xs40-manualv1_ 4.pdf. [ Links ]

10. LabVIEW User Manual, January edition, Dallas, National Instruments Corporation, 1998, 540pp. [ Links ]

11. LabVIEW Básico I. Manual del Curso versión 4.0, edición diciembre, Dallas, National Instruments Corporation, 1998, 416pp. [ Links ]

uBio

uBio